射频易商城_芯片电容_检测微小电容的测频专用芯片⑧

Https://www.RFeasy.cn

导读:很多朋友不知道芯片电容的检测,如何选择芯片电容。射频易商城RFeasy.cn为你解答芯片电容的检测

射频易商城 RFeasy.cn 隶属于电科益储供应链管理(成都)有限公司 旗下的国产化替代解决方案、专业射频微波器材一站式商城。

# 射频易商城 RFeasy.cn 芯片电容库存详情

https://www.rfeasy.cn/category/ld/ldc/

用于微小电容检测的测频专用芯片

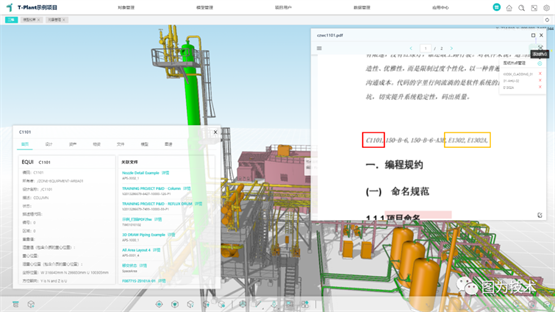

在CMOS集成屯路设计中, 带有反向操作的逻辑门要比相应的无反向操作的逻辑门少用两个晶体管, 而且速度更决, 所以将F“): 拍(r)・声O)化简成上面所示形式。 通过观察该式, 很容易得到同步脉冲产生器的逻辑电路原理图如图3—5所示。在数字设计巾, 可综合的延时方法有:

一使信号经过逻辑门得到延时(如非门);一使用器件提供的延时单元

一用适当的时钟驱动移位寄存器

当使用多级非门的时候综合器往往会将其优化掉, 因为综合器会认为偶数个 非门级联足冗余逻辑。 现在可以在综台工具的选项中设置保持层次、 禁止优化逻 辑。 这样, 非门就不会被综合工具优化掉。 用器件自带的延时单元也可以产生延 时, 忸是这样形成的延时在FPGA芯片中并不稳定, 会随着温度等外部条件的变 化而改变, 因而不太提倡。 用适当的时钟来驱动移位寄存器, 待延时信号作数据 输入, 按所需延时正确设置移位寄存器的级数, 移位寄存器的输出即为延时后的 信号。 此方法产生的延时信号与原信号比有误差, 误差大小由时钟的周期来决定。 对于数据信号的延时, 在输出端用数据时钟剥延时后信号重新采样, 就可以消除 误差。

3. 3. 2控制器

控制器的功能是完成如图3—7所示的时序, 它为计数器产生清零和使能信号。丁为预置闸门信号, syn—out为同步脉冲, c肛为图3-1中所示的计数器A、 计数器B的清零信号, 而e/l为这两个计数器的使能信号。 其中, cfr和e/,/均为高电平图3. 7控制器工作时序有效。 观察图3. 7, Z的上升沿到来时, 立刻将c扫置为高电平直到丁上升沿后的第一个同步脉冲出现时c咖变成低电平。 c肛变为低电平的同时, en被置为高电平直到z的下降沿后的个同步脉冲出现时e, l变为低电平。

推荐产品一、丽芯微电10000pF, ≥1G@25V, 双面不留边 单层芯片电容 型号:C11-90-25V-103 推荐产品二、丽芯微电1000pF, ≥1G@50V, 双面不留边 单层芯片电容 型号:C11-30-50V-102 射频易商城 官方自营、100%测试;

容值/容差:10000pF / ±20%

温度系数:±15%@-55~+125℃

绝缘电阻@电压:≥1G@25V

损耗@频率:≤2.5@1MHz

封装尺寸:2.290*2.290*0.178 mm

性能特点:尺寸小、容值大,结构简单,电极正面及反面均不留绝缘边;采用MM结构,产品寄生参数小,使用频率高至100GHz;表面纯金电极,适合金丝、金带等微组装工艺;适合Au/Sn、Au/Si、Au/Ge 共晶焊,以及Sn /Pb、导电胶粘接;七专级/ 普军级可选。

容值/容差:1000pF / ±20%

温度系数:±15%@-55~+125℃

绝缘电阻@电压:≥1G@50V

损耗@频率:≤2.5@1MHz

封装尺寸:0.762*0.762*0.178 mm

性能特点:尺寸小、容值大,结构简单,电极正面及反面均不留绝缘边;采用MM结构,产品寄生参数小,使用频率高至100GHz;表面纯金电极,适合金丝、金带等微组装工艺;适合Au/Sn、Au/Si、Au/Ge 共晶焊,以及Sn /Pb、导电胶粘接;七专级/ 普军级可选。

科研、院校等单位可申请5-100万预授信(联系客服)

射频易商城(成都仓库)发货,并提供售后服务

晶体振荡器 芯片电容 低噪声放大器 功率放大器