射频易商城_芯片电容_如何制备高介薄型陶瓷芯片电容⑤

Https://www.RFeasy.cn

导读:很多朋友不知道芯片电容中的高介薄型陶瓷芯片电容制备工艺研究,如何选择芯片电容。射频易商城RFeasy.cn为你解答芯片电容中的高介薄型陶瓷芯片电容制备工艺研究

射频易商城 RFeasy.cn 隶属于电科益储供应链管理(成都)有限公司 旗下的国产化替代解决方案、专业射频微波器材一站式商城。

高介薄型陶瓷芯片电容制备工艺研究⑤

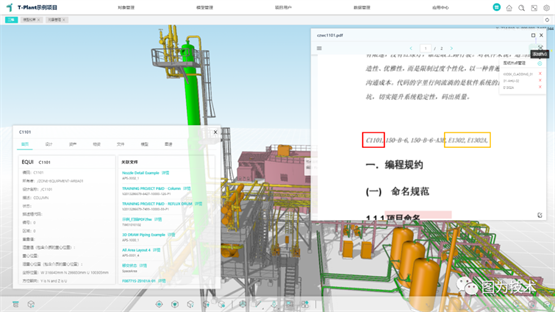

2. 2 过渡层厚度对器件性能的影响

选用 HT 作为陶瓷介质基片, 由 于复合膜层( 如 TaN/TiW、 TiW/Ni) 不易准确分解各层的厚度, 会使 测试数据出现错误。 因此针对过渡层厚度对器件性能 影响的分析, 高介薄型陶瓷芯片电容的制备选择温度 稳定性较好、 制备难度较低的 TiW/Au 膜系, 通过控 制溅射的参数, 使过渡层的厚度分别为 80, 400, 600 nm, 种子层溅射完成后观察表面覆盖情况, 然后进行 外金属电极制备和分片切割, 最后测量高介薄型陶瓷 芯片电容的性能。2. 2. 1 不同过渡层厚度样品表面覆盖情况

在溅射完成后, 通过 SEM 观察样品表面, 不同厚 度过渡层对应样品表面的 SEM 图如图 6。 从图 6 ( a) 可以看出, 采用 80 nm 厚度过渡层制备 的电容样品表面膜层覆盖不完全, 表面有明显的陶瓷 介质晶粒。 当过渡层厚度增加至 400 nm 时, 电容样品 表面覆盖情况有明显改善, TiW 层将陶瓷表面包裹完 全, 基本看不见裸露在外的陶瓷晶粒, 充分阻断了表

面金属电极与陶瓷介质的接触。 再将缓冲层厚度提高到 600 nm 后, 电容样品表面包裹覆盖情况进一步提高, 已经完全看不到裸露在外的陶瓷晶粒, 而且也看不见晶粒的轮廓, 整个缓冲层表面平整、 光滑且致密。因此从膜层覆盖的情况来看, 膜层厚度在 400 nm 时已经能比较好地覆盖介质陶瓷, 当增加到 600 nm 后, 表面覆盖更加完整, 已基本看不到表面晶粒的轮廓。

推荐产品一、丽芯微电 100pF, ≥1G@50V, 单面留边 单层芯片电容

型号:C12-15-50V-101

容值/容差:100pF / ±20%

温度系数:±15%@-55~+125℃

绝缘电阻@电压:≥1G@50V

损耗@频率:≤2.5@1MHz

封装尺寸:0.381*0.381*0.178 mm

性能特点:尺寸小、容值大,结构简单,单面电极留有绝缘边;采用MM结构,产品寄生参数小,使用频率高至100GHz;表面纯金电极,适合金丝、金带等微组装工艺;适合Au/Sn、Au/Si、Au/Ge 共晶焊,以及Sn /Pb、导电胶粘接;七专级/ 普军级可选。

推荐产品二、丽芯微电 10pF, ≥100G@100V, 单面留边 单层芯片电容

型号:C12-15-100V-100

容值/容差:10pF / ±20%

温度系数:±15%@-55~+125℃

绝缘电阻@电压:≥100G@100V

损耗@频率:≤4.0@1KHz

封装尺寸:0.381*0.381*0.178 mm

性能特点:尺寸小、容值大,结构简单,单面电极留有绝缘边;采用MM结构,产品寄生参数小,使用频率高至100GHz;表面纯金电极,适合金丝、金带等微组装工艺;适合Au/Sn、Au/Si、Au/Ge 共晶焊,以及Sn /Pb、导电胶粘接;七专级/ 普军级可选。

射频易商城 官方自营、100%测试;

科研、院校等单位可申请5-100万预授信(联系客服)

射频易商城(成都仓库)发货,并提供售后服务

衰减器 巴伦 滤波器